В данной статье описывется изучение и построение логических схем на простых логических элементах.

Электронными приборами называются активные вакуумные, газоразрядные и полупроводниковые элементы электрических цепей. Наряду с пассивными элементами (резисторами, катушками индуктивности и конденсаторами) они входят в электрические схемы устройств, в которых происходит преобразование электромагнитной энергии и сигналов. Наиболее простым видом преобразования является выпрямление переменного тока, более сложным — инвертирование постоянного тока в переменный, усиление, генерирование и преобразование сигналов сложной формы. Различают вакуумные и полупроводниковые электронные приборы. В полупроводниковых приборах электрические токи текут в твердом теле — полупроводниках. Поэтому их часто называют твердотельными электронными приборами. К ним относятся полупроводниковые диоды, триоды (транзисторы), тиристоры, светодиоды, фоторезисторы, фототранзисторы. Полупроводниковые электронные приборы наиболее часто используются в современных электронных устройствах.

Логические схемы - физические устройства, реализующие функции математической логики. Логические схемы подразделяются на комбинационные схемы (схемы без памяти) и последовательные схемы (схемы с памятью). Логические схемы являются основой любых систем обработки дискретной информации.

Логический элемент — элемент, осуществляющий определенные логические зависимость между входными и выходными сигналами. Логические элементы обычно используются для построения логических схем вычислительных машин, дискретных схем автоматического контроля и управления. Для всех видов логических элементов, независимо от их физической природы, характерны дискретные значения входных и выходных сигналов.

Логические элементы имеют один или несколько входов и один или два (обычно инверсных друг другу) выхода. Значения «нулей» и «единиц» выходных сигналов логических элементов определяются логической функцией, которую выполняет элемент, и значениями «нулей» и «единиц» входных сигналов, играющих роль независимых переменных. Существуют элементарные логические функции, из которых можно составить любую сложную логическую функцию («И», «ИЛИ», «НЕ» и «исключающее ИЛИ»).

В полупроводниковых приборах в качестве уровня используются соответствующие значения напряжения. Например, в ТТЛ схемах при Uпит = 5В низкий уровень составляет 0…1,8В (16% Uпит), высокий – 2…5В.

1. Синтез комбинационной логической схемы

1.1 Составление таблицы истинности

Исходя из задания, было дано следующее условие для построения комбинационной логической схемы:

Y = (1, 2, 3, 5, 7, 12)

Таблица истинности будет выглядеть следующим образом:

Таблица 3.1 - Таблица истинности

|

|

Состояние входов |

Варианты выходных состояний |

|||

|

a |

b |

c |

d |

y |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

2 |

0 |

0 |

1 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

0 |

|

7 |

0 |

1 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

0 |

|

10 |

1 |

0 |

1 |

0 |

0 |

|

11 |

1 |

0 |

1 |

1 |

0 |

|

12 |

1 |

1 |

0 |

0 |

1 |

|

13 |

1 |

1 |

0 |

1 |

0 |

|

14 |

1 |

1 |

1 |

0 |

0 |

|

15 |

1 |

1 |

1 |

1 |

0 |

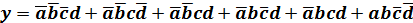

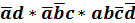

Алгебраическое выражение ДНФ записывается в виде:

1.2 Минимизация логической функции

Для минимизации логической схемы следует применить метод карт Карно.

Карта Карно — графический способ представления переключательных булевых функций с целью наглядной и удобной их минимизации, обеспечивающий упрощение сложных логических функций многих переменных. Основным методом минимизации логических функций, представленных в виде ДНФ или КНФ, является операция попарного неполного склеивания и элементарного поглощения. Операция попарного склеивания осуществляется между двумя термами (членами), содержащими одинаковые переменные, вхождения которых (прямые и инверсные) совпадают для всех переменных, кроме одной. В этом случае все переменные, кроме одной, можно вынести за скобки, а оставшиеся в скобках прямое и инверсное вхождение одной переменной подвергнуть склейке.

Применив данный метод к условию, получаем следующую схему:

|

|

|

|

|

|

|

|

|

|

|

|

|

ab |

|

|

|

1 |

|

|

|

1 |

1 |

|

|

|

|

1 |

1 |

|

Парные элементы объединены в группы.

Исключив члены, дополняющие друг друга внутри контура, получим минимизированную функцию:

y =

Минимизацию схем целесообразно применять, для уменьшения стоимость конечных устройств, а также их уменьшения. Так как для реализации одной и той же функции требуется, очевидно, гораздо меньше элементов.

1.3 Построение комбинационной логической схемы с использованием элементов «И», «ИЛИ», «НЕ»

«И» - логический элемент, выполняющий над входными данными операцию конъюнкции или логического умножения. Данный элемент может иметь от 2 до 8 (наиболее распространены в производстве элементы «И» с 2, 3, 4 и 8 входами) входов и один выход.

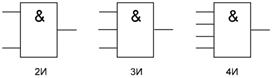

Рисунок 1.1 – графическое обозначение элемента «И»

Условные обозначения логических элементов «И» с разным количеством входов приведены на рисунке. Далее логический элемент «И» с тем или иным числом входов обозначается как «2И», «4И» и т. д. - элемент «И» с двумя входами, с четырьмя входами и т. д.

|

Вход Х1 |

Вход Х1 |

Выход Y |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

Таблица 1.1 - таблица истинности для элемента «И»

Таблица истинности для элемента «И» показывает, что на выходе элемента будет логическая единица лишь в том случае, если логические единицы будут одновременно на первом входе «И» на втором входе. В остальных трех возможных случаях на выходе будет ноль.

Обозначается элемент «И» как прямоугольник с закруглением на выходе или как прямоугольник с символом «1».

«ИЛИ» - логический элемент, выполняющий над входными данными операцию дизъюнкции или логического сложения. Он так же, как и элемент «И» выпускается с двумя, тремя, четырьмя и т. д. входами и с одним выходом.

|

Вход Х1 |

Вход Х1 |

Выход Y |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Таблица 1.2 - таблица истинности для элемента «ИЛИ»

Таблица истинности для элемента «ИЛИ» показывает, что для появления на выходе логической единицы, достаточно чтобы логическая единица была на первом входе ИЛИ на втором входе. Если логические единицы будут сразу на двух входах, на выходе также будет единица.

Обозначается элемент «ИЛИ» как закругление на входе и закругление с заострением на выходе или как прямоугольник с символом «1».

«НЕ» - логический элемент, выполняющий над входными данными операцию логического отрицания. Данный элемент, имеющий один выход и только один вход, называют еще инвертором, поскольку он на самом деле инвертирует (обращает) входной сигнал.

|

Вход Х |

Выход Y |

|

0 |

1 |

|

1 |

0 |

Таблица 1.3 - таблица истинности для элемента «НЕ»

Таблица истинности для инвертора показывает, что высокий потенциал на входе даёт низкий потенциал на выходе и наоборот.

Обозначается элемент «НЕ» в форме треугольника с кружочком на выходе или как прямоугольник с символом «1», с кружком на выходе.

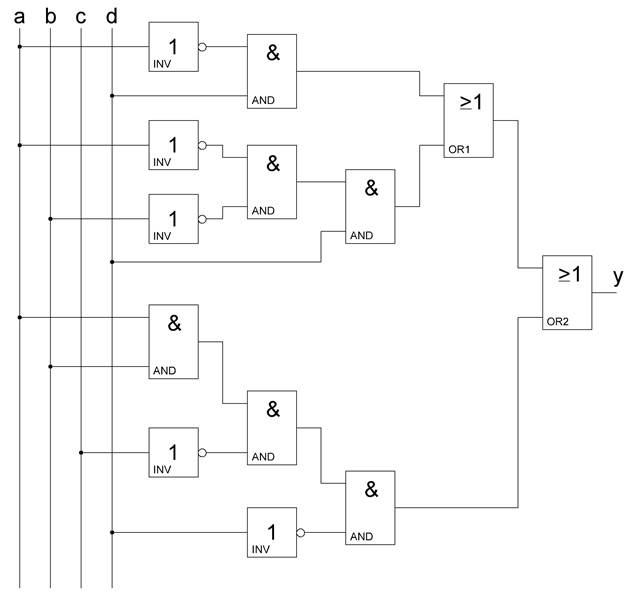

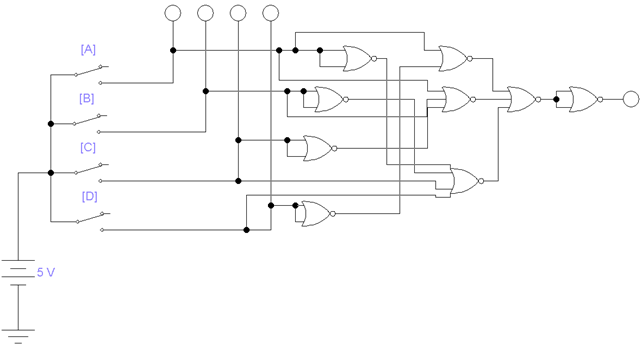

Согласно условию, была получена следующая схема, с использованием логических элементов «И», «ИЛИ», «НЕ», на основе минимизированной функции:

Рисунок 1.2 - Комбинационная логическая схема

с использованием элементов «И», «ИЛИ», «НЕ»

2. Синтез комбинационной логической схемы с использованием логических элементов «И-НЕ», «ИЛИ-НЕ»

2.1 Построение комбинационной логической схемы с использованием элементов «И-НЕ»

«И-НЕ» - логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Другими словами, это элемент «И», дополненный элементом «НЕ».

|

Вход Х1 |

Вход Х1 |

Выход Y |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Таблица 2.1 - таблица истинности для элемента «И-НЕ»

Таблица истинности для элемента «И-НЕ» противоположна таблице для элемента «И». Вместо трех нулей и единицы — три единицы и ноль. Элемент «И-НЕ» называют еще «элемент Шеффера» в честь математика Генри Мориса Шеффера, впервые отметившего значимость этой логической операции в 1913 году. Обозначается как «И», только с кружочком на выходе.

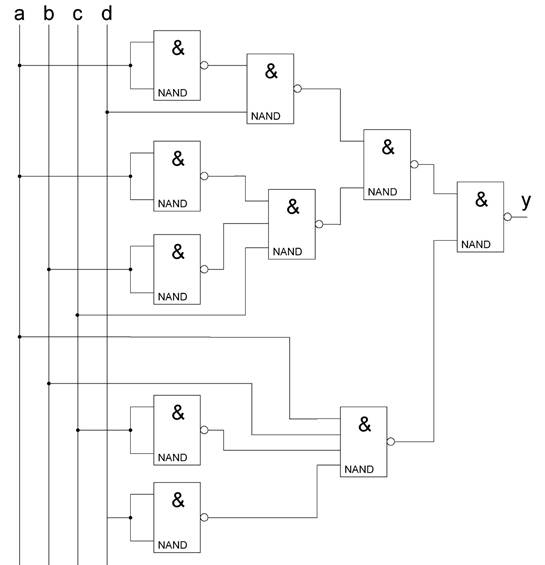

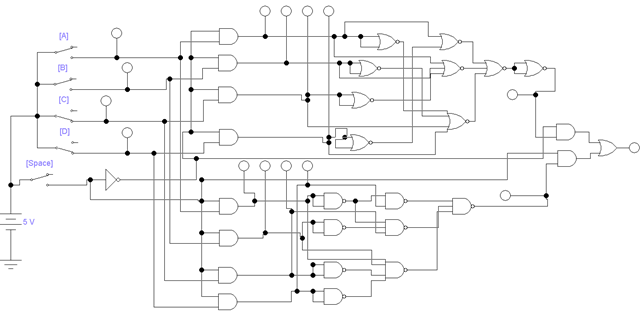

Согласно условию, была получена следующая схема, на основе минимизированной функции:

Рисунок 2.1 - Комбинационная логическая схема

с использованием элементов «И-НЕ»

2.2 Построение комбинационной логической схемы с использованием элементов «ИЛИ-НЕ»

«ИЛИ-НЕ» - логический элемент, выполняющий над входными данными операцию логического сложения, и затем операцию логического отрицания, результат подается на выход. Иначе говоря, это элемент «ИЛИ», дополненный элементом «НЕ» - инвертором. На рисунке приведено условное обозначение логического элемента «2ИЛИ-НЕ».

|

Вход Х1 |

Вход Х1 |

Выход Y |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Таблица 2.2 - таблица истинности для элемента «ИЛИ-НЕ»

Таблица истинности для элемента «ИЛИ-НЕ» противоположна таблице для элемента «ИЛИ». Высокий потенциал на выходе получается лишь в одном случае - на оба входа подаются одновременно низкие потенциалы.

Обозначается как «ИЛИ», только с кружочком на выходе, обозначающим инверсию.

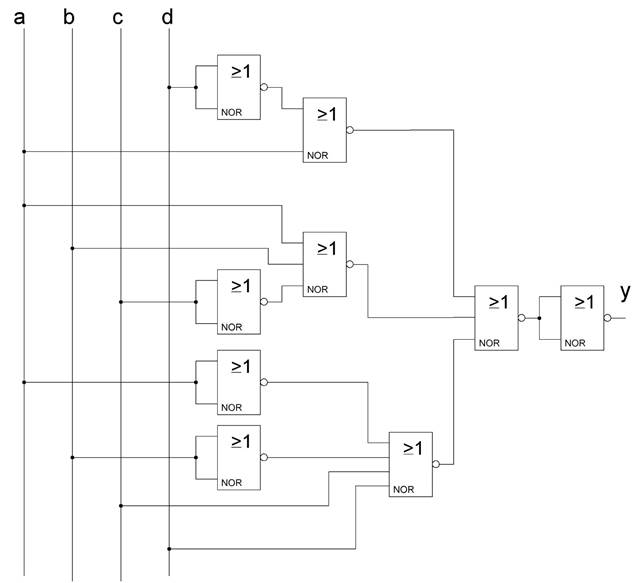

Согласно условию, была получена следующая схема, на основе минимизированной функции:

Рисунок 2.2 - Комбинационная логическая схема

с использованием элементов «ИЛИ-НЕ»

3. Синтез комбинационной логической схемы с использованием логических элементов «И-НЕ», «ИЛИ-НЕ» с использованием мультиплексора

Мультиплексором — называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX (от англ. multiplexor), а также через MS (от англ. multiplex or selector).

Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства.

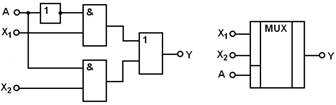

Рисунок 3.1 - Схема и графическое обозначение мультиплексора

Основой данной схемы являются две схемы совпадения на элементах «И», которые при логическом уровне «1» на одном из своих входов повторяют на выходе то, что есть на другом входе.

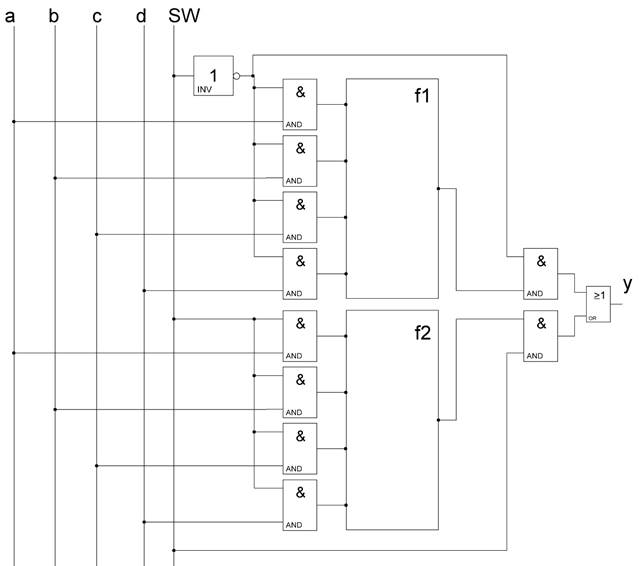

Переключение работы функций осуществляется подачей логического сигнала на шину SW. В зависимости от сигнала «0» или «1» будет включена в работу соответствующая функция. Переключение работы функций осуществляется как по входным сигналам, так и по выходным.

Рисунок 3.2 - Логическая схема мультиплексора

4. Исследование электронных схем методом моделирования в симуляторе

Моделирование всех схем производилось в симуляторе Electronics Workbench.

Electronics Workbench – один из самых известных пакетов схематического моделирования цифровых, аналоговых и аналогово-цифровых электронных схем различной степени сложности.

Данная система схемотехнического моделирования показала достаточно высокую гибкость и точность вычислений, найдя широкое применение, как на предприятиях, так и в высших учебных заведениях. Он включает инструменты для моделирования, редактирования, анализа и тестирования электрических схем. Программа имеет простой интерфейс и идеально подходит для начального обучения электронике. Библиотеки предлагают огромный набор моделей радиоэлектронных устройств от самых известных иностранных производителей с широким диапазоном значений параметров. Кроме этого, есть возможность создания собственных компонентов. Активные элементы могут быть показаны как идеальными, так и реальными моделями. Всевозможные приборы (мультиметры, осциллографы, вольтметры, амперметры, частотные графопостроители, динамики, светодиоды, лампы накаливания, логические анализаторы, сегментные индикаторы) позволяют делать измерения любых величин, строить графики.

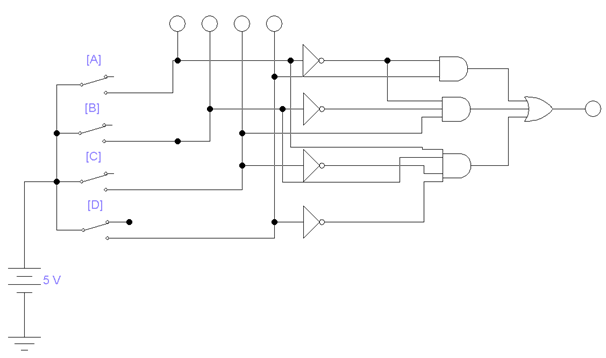

Моделирование комбинационной логической схемы с использованием элементов «И», «ИЛИ», «НЕ»:

Рисунок 4.1 - Схема электрическая принципиальная

с использованием элементов «И», «ИЛИ», «НЕ»

Моделирование комбинационной логической схемы с использованием элементов «И-НЕ»:

Рисунок 4.2 - Схема электрическая принципиальная

с использованием элементов «И-НЕ»

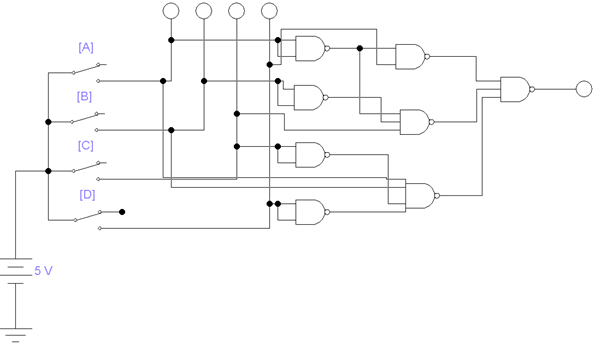

Моделирование комбинационной логической схемы с использованием элементов «ИЛИ-НЕ»:

Рисунок 4.3 - Схема электрическая принципиальная

с использованием элементов «ИЛИ-НЕ»

Моделирование комбинационной логической схемы с использованием мультиплексора для переключения схем «И-НЕ» и «ИЛИ-НЕ»:

Рисунок 4.4 - Схема электрическая принципиальная

с использованием мультиплексора

В процессе симулирования, на вход испытуемых схем были поданы все комбинации сигналов из приведенной таблице истинности. На выходе схемы были получены верные сигналы, соответствующие условию задания.

Подача сигналов осуществляется переключением переключателей A, B, C, D, которые позволяют вставить логические сигналы «0» и «1». Контроль за состоянием сигналов можно осуществлять по индикаторным лампам.

На схеме с мультиплексором, для переключения состояния используется клавиша «пробел». Так как обе схемы описывают одну и ту же логику – вне зависимости от переключения мультиплексора, выходной результат будет одинаковый.

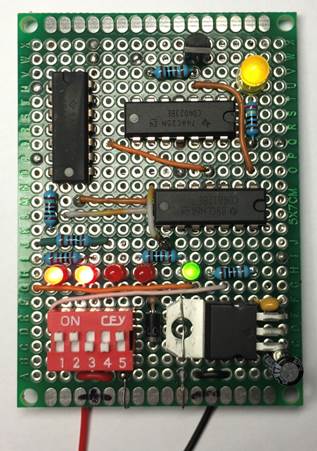

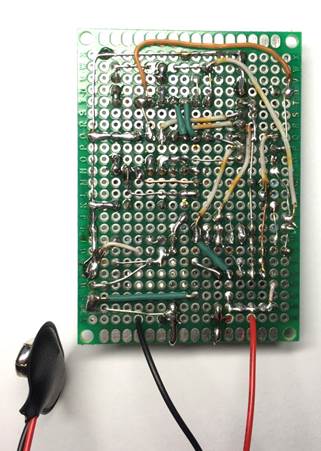

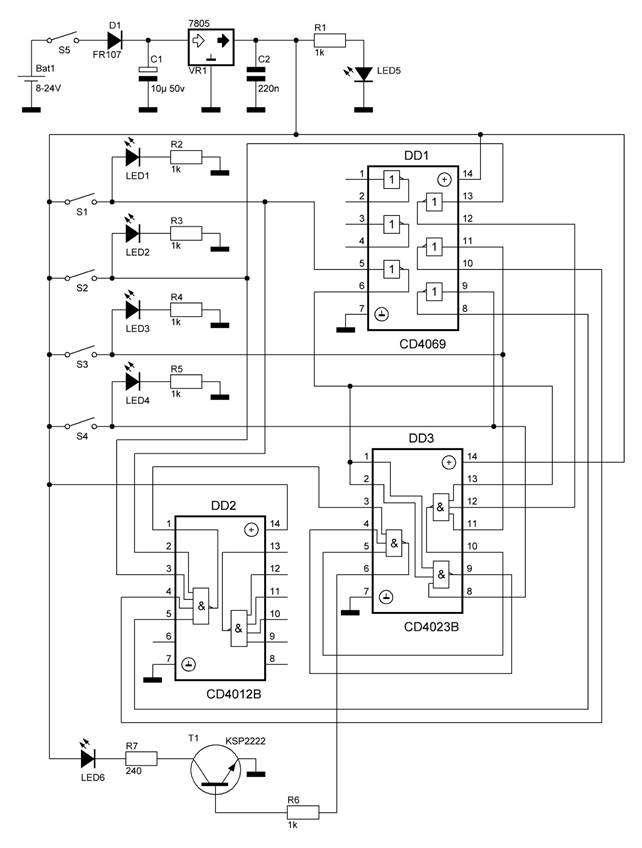

Дополнительно для проверки работоспособности разработанной схемы была построена реальная модель устройства на основе имеющихся в наличии микросхем логики «НЕ», «И-НЕ» серии CD4000B с буферизированным выходом. Схема построена на базе схемы с элементами «И-НЕ».

Полная принципиальная схема устройства приведена ниже. Она состоит из: источника питания напряжением от 8 до 24 вольт; переключателей и индикаторных светодиодов для отображения состояния логических сигналов; микросхем логики; транзистора в качестве ключа включения индикаторного светодиода на выходе логической функции; ограничительных резисторов.

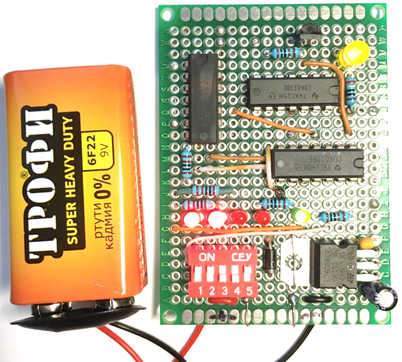

Устройство выполнено на макетной плате. Все элементы соединены дорожками и перемычками в соответствии со схемой.

|

|

|

|

|

|

Рисунок 4.6 - принципиальная схема устройства

Для реализации логической функции потребовались 3 комбинированных микросхем.

В качестве инвертора сигналов DD1 применилась микросхема CD4069 (6НЕ), так как была в наличии. Она состоит из 6 независимых логических элемента «НЕ». В этом случае понадобится задействовать только 4 её элемента. В качестве аналога, можно было применить для инвертора микросхему CD4011B (4И-НЕ) с соединенными парами входов у каждого элемента.

Для реализации логики применялись две микросхемы: CD4012B (2И-НЕ) и CD4023B (3И-НЕ). CD4012B представляет собой два элемента И-НЕ с 4 входами, а CD4023B – три элемента «И-НЕ» с 3 входами. Элементы DD1, DD2, DD3 соединены между собой в соответствии с полученной функцией по заданию. Так как микросхемы в своем составе содержат несколько элементов, некоторые из них остались не задействованы.

Параметры у данной серии микросхем следующие: напряжение питания 3-8В; низкий логический уровень 1.5-4В; высокий логический уровень 3.5-11В.

Для индикации логических сигналов применены светодиоды LED1-6 с ограничивающими ток резисторами. По результатам замеров тока светодиодов было выяснено, что для индикаторов (3мм) LED1-5 – A, B, C, D и питания, достаточно тока около 5мА, а для выходного индикатора (5мм) LED6 – 12мА. При напряжении 5В были применены резисторы в 1 кОм и 240 Ом соответственно.

Для управления включением выходного светодиода, в качестве ключа, был применен маломощный биполярный транзистор npn-структуры T1, типа KSP2222A.

Питание построено на базе линейного стабилизатора напряжения VR1 типа LM7805 с фиксированным выходным напряжением 5 вольт. Его характеристики: максимальное входное напряжение 35В; выходное напряжение 5В; максимальный ток нагрузки 1.5А. Для фильтрации возможных импульсов по питанию были применены конденсаторы до и после стабилизатора. Применение стабилизированного напряжения 5В дает возможность напрямую использовать это напряжение для логического «1».

Так как устройство не имеет собственного источника питания, для защиты от переполюсовки применяется последовательно включенный диод D1. Падением напряжения на нем в данном случае можно пренебречь.

Питание схемы осуществляется от батареи типа «КРОНА» напряжением 9В или любого другого источника питания с напряжением от 8 до 24В. Потребляемый ток во время работы составляет около 35мА.

Работает устройство следующим образом. Для включения, необходимо перевести переключатель S5 в положение «ON». Светодиод LED5 зеленого цвета будет говорить о включении устройства. Комбинация входных логических сигналов осуществляется переключателями S1-4, а контроль их положений индицируют красные светодиоды LED1-4. Светодиод желтого цвета LED6 отображает состояние выходного сигнала с данной функции, в зависимости от поданных на нее входных сигналов. Свечение светодиодов означают присутствие логического сигнала «1», а отсутствие свечения – «0».

Для проверки корректности работы был осуществлен тест, в котором на вход схемы были поданы все сигналы из приведенной таблицы истинности, а на выходе схемы были получены те же сигналы, в соответствии с заданием.

Рисунок 4.7 – общий вид устройства

Литература

1. Ширин, И.Я. Схемотехника аналоговых и цифровых устройств: Учебное пособие для ву- зов.- Минск: БНТУ, 2005. - 309 с.

2. Основы электронной техники: Элементы, схемы, системы: [Краткая энциклопедия по электронике] 2-е изд./ К.Ф. Ибрагим; Пер. В.М. Матвеев, Г.Ф. Хохлов и Ф.Г. Хохлов / Под ред. Н.И. Аникушина М.: Мир, 2001. - 397 с.

3. Гусев, В. Г. Электроника / В. Г. Гусев, В. М. Гусев. - М: Высш. шк.,2000.-621 с.

4. Хоровиц, П. Искусство схемотехники. / П. Хоровиц, У. Хилл; пер. с англ. Б. Н. Бронин [и др.]; - М., Мир, 2001. - 704 с.

1

1